用AI指导芯片设计,中科大王杰教授团队、华为诺亚实验室、天津大学提出全新芯片宏单元布局优化方法LaMPlace!

以前芯片设计可能是先放好再看效果,现在LaMPlace 能在“放”的时候就考虑最终性能,比如电路运行速度怎么样(WNS、TNS这些指标),这样能省掉后面很多麻烦,让整个设计流程更快、更高效。

这为推进国产EDA工具的智能化、提速设计流程提供助力,也推动了芯片设计行业的“提前优化”趋势。

该论文已入选ICLR 2025 Oral。

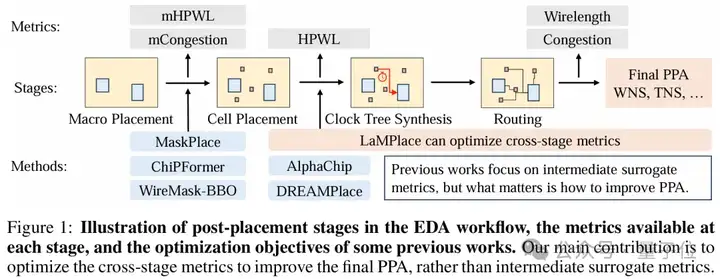

在现代芯片设计流程中,宏单元布局(Macro Placement) 是逻辑综合之后首个面向物理设计的关键环节。它决定了大块 IP(如存储器、接口、硬核模块)在芯片平面上的空间位置,对后续的标准单元布局、时钟树综合(CTS)、布线等环节具有重要影响,从而决定芯片的时序性能、功耗与面积(PPA)表现。其中 Worst Negative Slack(WNS)与 Total Negative Slack(TNS)这类跨阶段物理指标,是衡量设计是否满足时序收敛、能否正常运行的最终标准。但由于这些指标往往依赖后续EDA流程才能计算,现有学习方法难以在布局阶段直接建模或优化它们。

现有工作大多采用如下中间指标作为优化目标,如基于宏计算的半周线长(macro HPWL)、密度(Density)或拥塞(Congestion)等。这些指标虽然计算方便,但与最终设计目标存在显著偏离,导致训练过程与实际优化目标不一致,从而限制了算法在真实芯片设计流程中的应用价值。

LaMPlace 的提出,正是为了打破这一Gap:通过引入结构可解释的指标预测器,引导布局搜索直接“对接最终目标”,实现芯片设计“左移优化”的新范式。

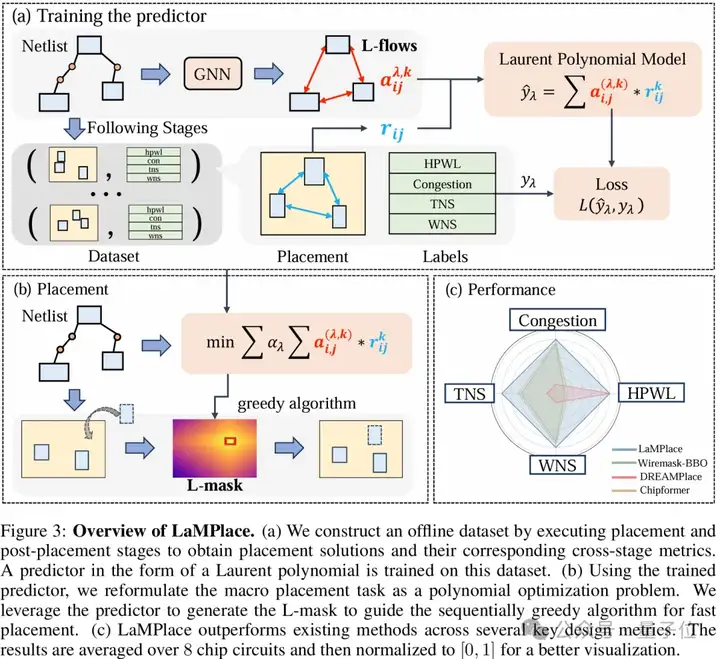

LaMPlace 构建了一个以“结构化预测 + 掩码生成 + 贪心放置”为主干的优化流程,能够将目标指标(如 WNS/TNS)的信息在布局阶段前移,作为放置决策的依据。

方法整体包括三个关键步骤:

离线训练一个预测器,输入为当前布局的宏单元位置分布,输出为多个跨阶段指标(如WNS、TNS等)的估计值;

将指标函数形式建模为宏间距离的多项式,所有系数可学习,保持高效计算与结构可解释性;

将预测器输出转化为二维掩码(mask),衡量每个候选位置对指标的影响,用作贪心式放置策略的搜索引导。

方法的整体框架如下图所示:

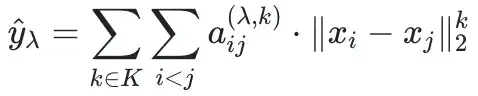

作者发现,EDA指标本质上依赖于宏之间的相对距离。因此,LaMPlace 将复杂的EDA指标形式表示成如下的Laurent多项式结构:

这种建模方式不仅提升了计算效率,更保留了指标对布局结构的可解释性。

借助上述预测结构,团队为每一个待放置宏生成一个二维掩码:

最终,通过贪心策略,在掩码上依次选址放置宏单元,构建高质量初始布局。

LaMPlace 不依赖特定搜索算法,它本质是一个mask引导模块,可嵌入现有系统中作为plug-in模块,与多种布局优化范式结合,例如黑盒优化器(BBO)、强化学习策略(RL)等。在实验中,作者展示了其与 WireMask-EA 框架 [3] 结合后的增益,验证了该方法的通用性。

LaMPlace 在标准芯片布局基准 ICCAD 2015 上展现了优异的性能,能够显著提升跨阶段关键指标如时序收敛性、拥塞等,且在未见过的新设计上依然保持稳定性能,体现出良好的泛化能力。

该方法具备良好的模块化特性,能够灵活嵌入现有布局优化框架中,成为推动EDA设计流程“左移优化”的有力工具。

LaMPlace 展示了一种结构建模与学习引导相结合的有效范式,为AI在芯片设计中的深入应用提供了新的思路。

本论文作者耿子介是中国科学技术大学MIRA实验室2022级博士生,师从王杰教授。此前,他于2022年毕业于少年班学院,取得数学与应用数学专业学士学位。他的主要研究方向包括机器学习在运筹优化与芯片设计等领域的应用、大语言模型等。他在NeurIPS、ICML、ICLR等人工智能顶级会议上发表论文十余篇,其中五篇论文入选Oral/Spotlight。他曾获2024年度国家奖学金;曾两次获得丘成桐大学生数学竞赛优胜奖;曾在微软亚洲研究院实习,获得“明日之星”称号;曾多次担任顶会审稿人,获评NeurIPS 2023 Top审稿人;参与创办南京真则网络科技有限公司。

论文地址:

openreview.net/pdf?id=YLIsIzC74j

文章来自于“量子位”,作者“LaMPlace团队”。